高云FPGA開發(fā)筆記(二) Gowin軟件與基礎(chǔ)開發(fā)流程詳解

一、引言

在上一期筆記中,我們初步認(rèn)識(shí)了高云(GOWIN)FPGA及其應(yīng)用場(chǎng)景。本期將聚焦于高云官方的FPGA開發(fā)軟件——Gowin云源軟件,并詳細(xì)介紹其基礎(chǔ)軟件開發(fā)流程,為后續(xù)的實(shí)戰(zhàn)項(xiàng)目打下堅(jiān)實(shí)基礎(chǔ)。

二、Gowin云源軟件概覽

高云FPGA的官方集成開發(fā)環(huán)境(IDE)是 Gowin云源軟件(Gowin YunYuan)。它是一個(gè)集設(shè)計(jì)輸入、綜合、布局布線、仿真和編程下載于一體的工具鏈。

- 主要組件:

- Gowin設(shè)計(jì)軟件(核心):包含工程管理、邏輯綜合、布局布線、比特流生成等核心功能。

- Gowin綜合器:將硬件描述語(yǔ)言(如Verilog HDL、VHDL)或原理圖轉(zhuǎn)換為門級(jí)網(wǎng)表。

- Gowin布局布線器:將網(wǎng)表映射到目標(biāo)FPGA芯片的具體邏輯資源上,并完成連線。

- 編程下載工具:生成最終的比特流文件,并通過下載器(如Gowin編程器)將其燒錄到FPGA芯片中。

- Gowin在線邏輯分析儀(GLA):一個(gè)強(qiáng)大的片上調(diào)試工具,無(wú)需額外IO引腳即可實(shí)時(shí)捕獲內(nèi)部信號(hào),極大方便了調(diào)試。

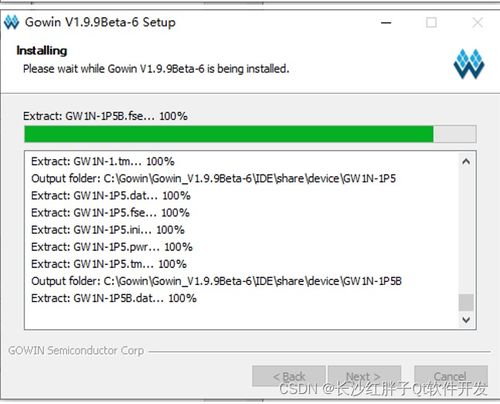

- 軟件獲取與安裝:

- 訪問高云半導(dǎo)體官方網(wǎng)站,在“支持”或“下載”頁(yè)面找到最新版本的Gowin云源軟件。

- 安裝過程簡(jiǎn)單,跟隨向?qū)Ъ纯伞0惭b完成后,首次啟動(dòng)可能需要申請(qǐng)(或已有)免費(fèi)的License文件進(jìn)行激活。高云為教育和中小規(guī)模設(shè)計(jì)提供了較為友好的授權(quán)策略。

三、高云FPGA基礎(chǔ)開發(fā)流程

一個(gè)完整的FPGA開發(fā)周期通常遵循以下步驟,在高云開發(fā)環(huán)境中也不例外:

第1步:創(chuàng)建新工程

啟動(dòng)Gowin軟件,通過“File -> New Project”創(chuàng)建工程。關(guān)鍵設(shè)置包括:

- 工程名稱與路徑:建議使用英文路徑。

- 選擇器件型號(hào):根據(jù)你手中的開發(fā)板(如小熊貓系列、GW1N系列等)準(zhǔn)確選擇FPGA的具體型號(hào)(如GW1N-LV4LQ144C6/I5)。

第2步:設(shè)計(jì)輸入

這是將設(shè)計(jì)構(gòu)思轉(zhuǎn)化為計(jì)算機(jī)可識(shí)別形式的關(guān)鍵一步,主要有三種方式:

- 硬件描述語(yǔ)言(HDL):最主流的方式。在軟件中“新建文件”,選擇Verilog或VHDL文件,編寫代碼描述電路功能。

- 原理圖輸入:對(duì)于小型或直觀的組合邏輯,可以通過繪制原理圖來完成。

- IP核調(diào)用:Gowin軟件提供了豐富的IP核資源(如PLL、存儲(chǔ)器、接口IP等),可以通過圖形化配置快速生成高性能模塊,極大提升開發(fā)效率。

第3步:邏輯綜合

點(diǎn)擊“Synthesis”按鈕或運(yùn)行相應(yīng)流程。綜合器將HDL代碼翻譯優(yōu)化成由基本邏輯門、觸發(fā)器、存儲(chǔ)器等組成的門級(jí)網(wǎng)表。此階段會(huì)檢查語(yǔ)法和基本邏輯錯(cuò)誤。

第4步:約束輸入

這是保證設(shè)計(jì)在物理硬件上正確運(yùn)行的必要環(huán)節(jié)。主要是通過編輯“.cst”約束文件來定義:

- 引腳約束:將設(shè)計(jì)中的輸入/輸出信號(hào)分配到FPGA芯片的具體物理引腳上,必須與開發(fā)板原理圖一致。

- 時(shí)序約束:定義時(shí)鐘頻率、輸入延遲、輸出延遲等,指導(dǎo)布局布線器優(yōu)化以實(shí)現(xiàn)時(shí)序收斂。

第5步:布局布線

點(diǎn)擊“Place & Route”按鈕。該步驟將綜合后的網(wǎng)表“放置”到FPGA芯片內(nèi)部的特定邏輯單元(如查找表LUT、寄存器)中,并在這些單元之間進(jìn)行物理“連線”。軟件會(huì)努力滿足你的時(shí)序約束。

第6步:生成編程文件

布局布線成功后,運(yùn)行“Generate Bitstream”。該過程會(huì)生成最終的可下載到FPGA的比特流文件(通常是.fs或.bit格式)。

第7步:下載與調(diào)試

使用高云編程器(或其他兼容下載器)連接開發(fā)板與電腦。

在軟件中打開“Program Device”工具,加載生成的比特流文件,將其燒錄至FPGA。

觀察開發(fā)板上的現(xiàn)象,驗(yàn)證功能。

若功能不符,需返回第2步進(jìn)行調(diào)試。強(qiáng)烈建議利用 Gowin在線邏輯分析儀(GLA) 進(jìn)行內(nèi)部信號(hào)抓取,這是定位問題最有效的手段之一。

四、新手實(shí)踐建議

- 從官方例程開始:高云軟件和開發(fā)板通常附帶豐富的示例工程,先運(yùn)行一個(gè)最簡(jiǎn)單的LED閃爍例程,走通整個(gè)流程。

- 重視約束文件:引腳分配錯(cuò)誤是新手最常見的導(dǎo)致“不工作”的原因,務(wù)必仔細(xì)核對(duì)。

- 善用GLA調(diào)試:比起盲目修改代碼,用GLA觀察實(shí)際信號(hào)能更快定位問題所在。

- 查閱官方文檔:高云官網(wǎng)提供的《用戶指南》、《數(shù)據(jù)手冊(cè)》和《IP核手冊(cè)》是解決問題的最佳參考資料。

五、

掌握Gowin云源軟件的基本操作和FPGA開發(fā)的標(biāo)準(zhǔn)流程,是開啟高云FPGA設(shè)計(jì)之旅的第一步。這個(gè)過程看似步驟繁多,但熟練后便會(huì)形成肌肉記憶。下一期,我們將通過一個(gè)具體的實(shí)戰(zhàn)項(xiàng)目——例如UART通信或PWM控制——來將本期的理論知識(shí)付諸實(shí)踐。

(注:本文基于特定版本軟件撰寫,實(shí)際操作請(qǐng)以您使用軟件的具體版本和官方最新文檔為準(zhǔn)。)

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.114office.com.cn/product/48.html

更新時(shí)間:2026-05-02 13:12:37